# **Advanced Computer Architecture**

Subject: ADVANCED COMPUTER ARCHITECTURE Credits: 4

#### **SYLLABUS**

## **Computer System**

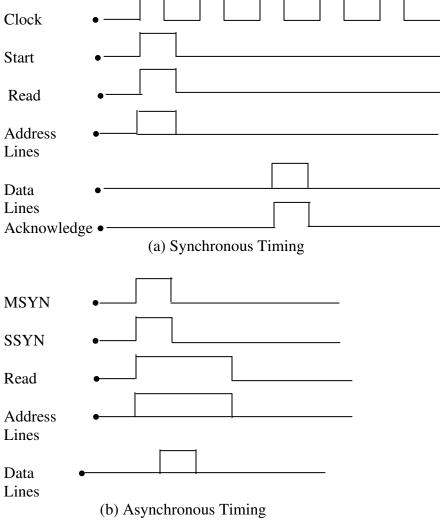

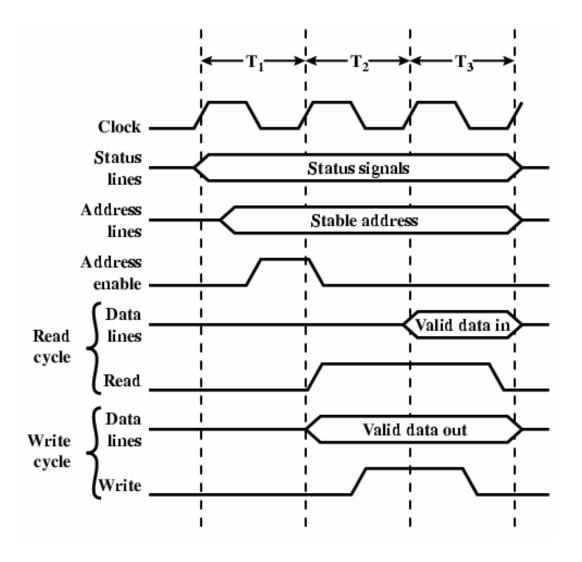

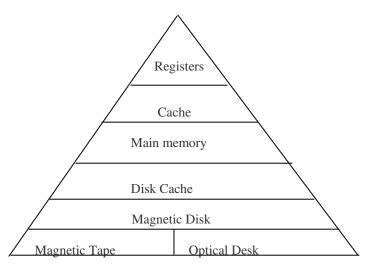

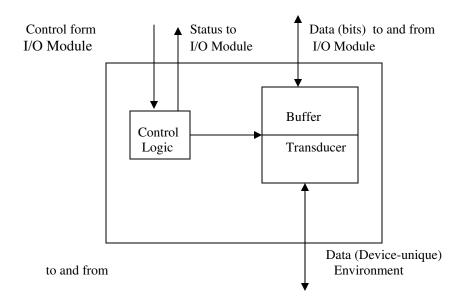

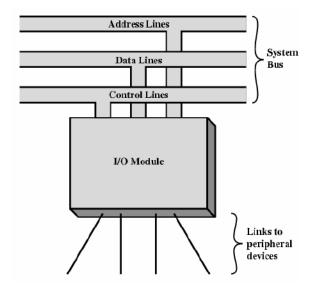

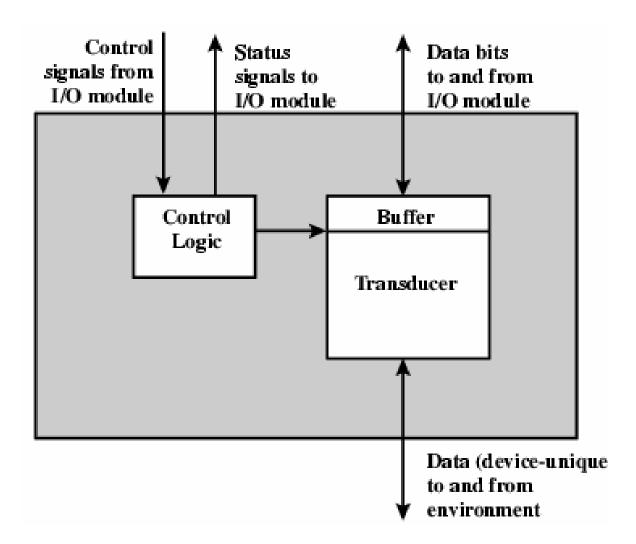

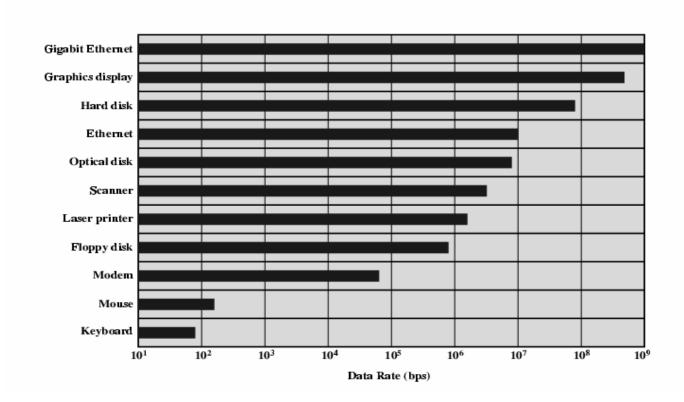

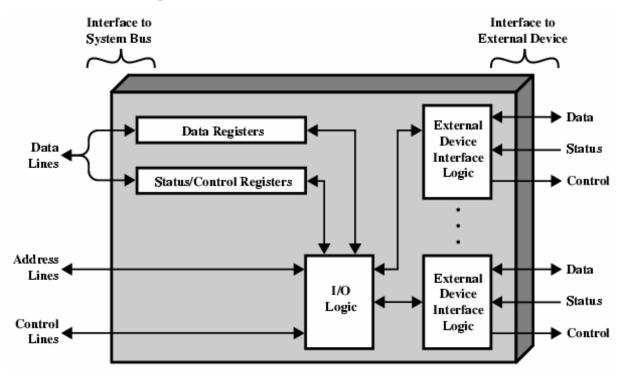

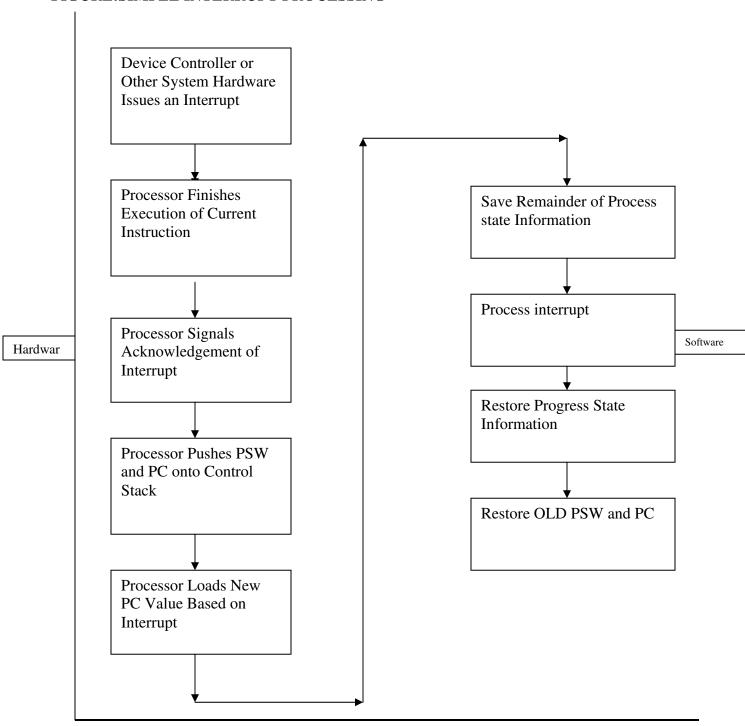

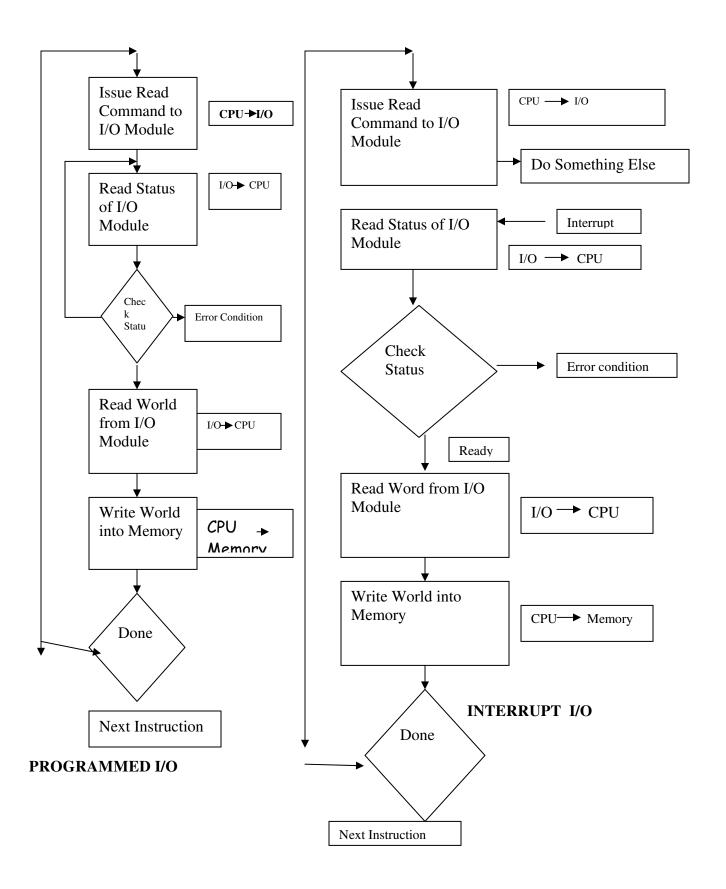

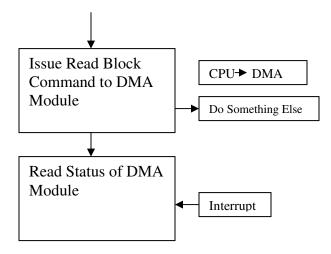

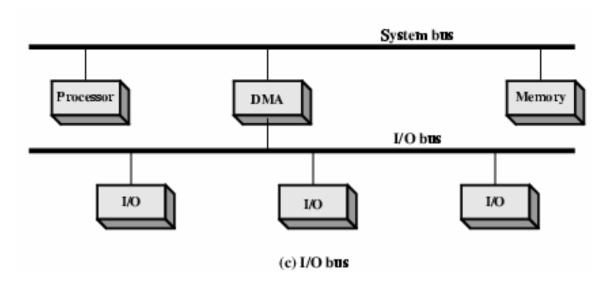

Generation of computers, Classification of computers, Organization, Structure and function, Von Neumann architecture. System bus, Bus Structure, Elements of Bus design (Type, Arbitration, Timing, Width, Data transfer Type), Interrupts, Instruction Cycle state Diagram with interrupts/Without interrupts, Characteristic of Internal memory (ROM, PROM, EPROM, Flash memory), Input / Output: (External / Peripheral Device, Function of I/O module, Programmer I/O, Interrupt Driver I/O DMA)

### **The Central Processing Unit**

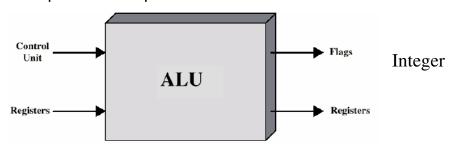

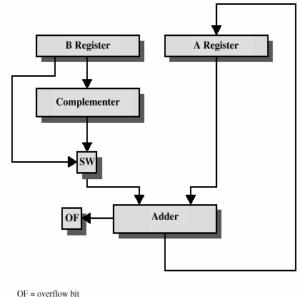

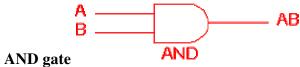

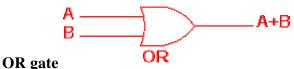

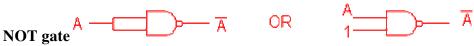

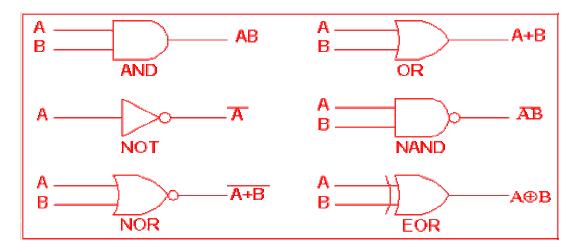

ALU, Binary Arithmetic, Floating point Arithmetic, Basic combinational and sequential Circuit Design, RTL representation,

Suggested Reading:

John L. Hennessy and David A. Patterson. *Computer Architecture: A Quantitative Approach* (Third Edition ed.). Morgan Kaufmann Publishers.

Laplante, Phillip A. (2001). Dictionary of Computer Science, Engineering, and Technology.

## Lecture 1

## **INTRODUCTION TO COMPUTERS**

## **Objectives of the lecture:**

1. To understand the basics of the computer.

Hello! Students, In today's information age, computers are being used in every occupation. They are used by people of all age and profession, in their work as well as their leisure. This new social age have changed the basic concept of 'Computing'. Computing, in today's information age, is no more limited to computer programmers and computer engineers. Rather than knowing how to program a computer, most computer users simply need to understand how a computer functions so in this lecture I will be discussing with you about this versatile tool, why is it so powerful and useful, its history and you will also be briefed about the classification of computers its devices in my today's lecture.

## What is A Computer?

A computer is an electronic machine that accepts information, stores it until the information is needed, processes the information according to the instructions provided by the user, and finally returns the results to the user. The computer can store and manipulate large quantities of data at very high speed, but a computer cannot think. A computer makes decisions based on simple comparisons such as one number being larger than another. Although the computer can help solve a tremendous variety of problems, it is simply a machine. It cannot solve problems on its own.

#### **History of Computers**

Since civilizations began, many of the advances made by science and technology have depended upon the ability to process large amounts of data and perform complex mathematical calculations. For thousands of years, mathematicians, scientists and businessmen have searched for computing machines that could perform calculations and analyze data quickly and efficiently. One such device was the abacus.

The abacus was an important counting machine in ancient Babylon, China, and throughout Europe where it was used until the late middle ages. It was followed by a series of improvements in mechanical counting machines that led up to the development of accurate mechanical adding machines in the 1930's. These machines used a complicated assortment of gears and levers to perform the calculations but they were far to slow to be of much use to scientists. Also, a machine capable of making simple decisions such as which number is larger was needed. A machine capable of making decisions is called a computer.

The first computer like machine was the **Mark I** developed by a team from IBM and Harvard University. It **used mechanical telephone relays** to store information and it processed data entered on punch cards. This machine was not a true computer since it could not make decisions.

In June 1943, work began on the world's first electronic computer. It was built at the University of Pennsylvania as a secret military project during World War II and was to be used to calculate the trajectory of artillery shells. It covered 1500 square feet and weighed 30 tons. The project was not completed until 1946 but the effort was not wasted. In one of its first demonstrations, the computer solved a problem in 20 seconds that took a team of mathematicians three days. This machine was a vast improvement over the mechanical calculating machines of the past because it used vacuum tubes instead of relay switches. It contained over 17,000 of these tubes, which were the same type tubes used in radios at that time.

The invention of the **transistor made smaller** and less expensive computers possible. Although computers shrank in size, they were still huge by today's standards. Another innovation to computers in the 60's was storing data on tape instead of punched cards. This gave computers the ability to store and retrieve data quickly and reliably.

## **Classification of Computers**

- Mainframe Computers

- Minicomputers

- Microcomputers

- Supercomputers

**Mainframe computers** are very large, often filling an entire room. They can store enormous of information, can perform many tasks at the same time, can communicate with many users at the same time, and are very expensive. The price of a mainframe computer frequently runs into the millions of dollars. Mainframe computers usually have many terminals connected to them. These terminals look like small computers but they are only devices used to send and receive information from the actual computer using wires. Terminals can be located in the same room with the mainframe computer, but they can also be in different rooms, buildings, or cities. Large businesses, government agencies, and universities usually use this type of computer.

**Minicomputers:** are much smaller than mainframe computers and they are also much less expensive. The cost of these computers can vary from a few thousand dollars to several hundred thousand dollars. They possess most of the features found on mainframe computers, but on a more limited scale. They can still have many terminals, but not as many as the mainframes. They can store a tremendous amount of information, but again usually not as much as the mainframe. Medium and small businesses typically use these computers.

**Microcomputers**: These computers are usually divided into desktop models and laptop models. They are terribly limited in what they can do when compared to the larger models discussed

above because they can only be used by one person at a time, they are much slower than the larger computers, and they cannot store nearly as much information, but they are excellent when used in small businesses, homes, and school classrooms. These computers are inexpensive and easy to use. They have become an indispensable part of modern life.

## **Computer Tasks**

- Input

- Storage

- Processing

- Output

#### When a computer is asked to do a job, it handles the task in a very special way.

- 1. It accepts the information from the user. This is called input.

- 2. It stored the information until it is ready for use. The computer has memory chips, which are designed to hold information until it is needed.

- 3. It processes the information. The computer has an electronic brain called the Central Processing Unit, which is responsible for processing all data and instructions given to the computer.

- 4. It then returns the processed information to the user. This is called output.

Every computer has special parts to do each of the jobs listed above. Whether it is a multimillion dollar mainframe or a thousand dollar personal computer, it has the following four components, Input, Memory, Central Processing, and Output.

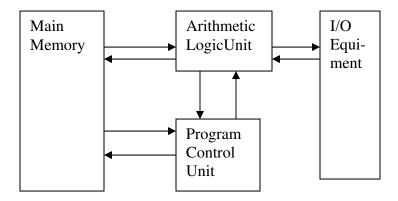

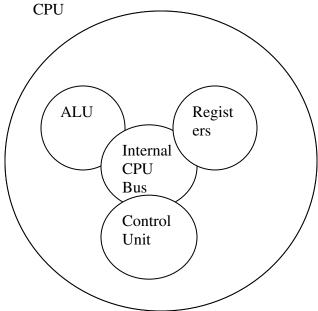

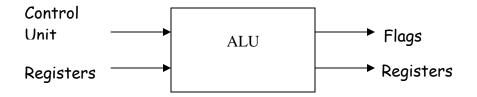

The central processing unit is made up of many components, but two of them are worth mentioning at this point. These are the arithmetic and logic unit and the control unit. The control unit controls the electronic flow of information around the computer. The arithmetic and logic unit, ALU, is responsible for mathematical calculations and logical comparisons.

## **Input Devices**

- Keyboard

- Mouse

- Scanner

- Microphone

- CD-ROM

- Joystick

## **Memory**

## Read Only Memory (ROM)

ROM is a small area of permanent memory that provides startup instructions when the computer is turned on. You can not store any data in ROM. The instructions in ROM are set by the manufacturer and cannot be changed by the user. The last instruction in ROM directs the computer to load the operating system.

Every computer needs an operating system. This is a special computer program that must be loaded into memory as soon as the computer is turned on. Its purpose is to translate your instructions in English into Binary so that the computer can understand your instructions. The operating system also translates the results generated by your computer into English when it is finished so that we can understand and use the results. The operating system comes with a computer.

## Random Access Memory (RAM)

This is the area of memory where data and program instructions are stored while the computer is in operation. This is temporary memory. <u>NOTE:</u> The data stored in RAM is lost forever when the power is turned off. For this reason it is very important that you save your work before turning off your computer. This is why we have peripheral storage devices like your computer's hard disk and floppy diskettes.

### **Permanent Memory (Auxiliary Storage)**

Your files are stored in permanent memory only when saved to your disk in a: drive or saved to your computer's hard disk, Drive c:

To better understand how a computer handles information and to also understand why information is lost if the power goes off, let's take a closer look at how a computer handles information. **Your** computer is made of millions of tiny electric circuits. For every circuit in a computer chip, there are two possibilities:

- 1. an electric circuit flows through the circuit or

- 2. An electric circuit does not flow through the circuit.

When an electric current flows through a circuit, the circuit is on. When no electricity flows, the circuit is off. An "on" circuit is represented by the number one (1) and an off circuit is represented by the number zero (0). The two numbers 1 and 0 are called bits. The **word bit comes from "binary digit".** Each time a computer reads an instruction, it translates that instruction into a series of bits, 1's and 0's. On most computers every character from the keyboard is translated into eight bits, a combination of eight 1's and 0's. Each group of eight bits is called a byte.

## Byte – The amount of space in memory or on a disk needed to store one character. 8 bits = 1 Byte

Since computers can handle such large numbers of characters at one time, metric prefixes are combined with the word byte to give some common multiples you will encounter in computer literature.

| Kilo means 1000          | kilobyte (KB) | = | 1000 Bytes          |

|--------------------------|---------------|---|---------------------|

| Mega means 1,000,000     | megabyte (MB) | = | 1,000,000 Bytes     |

| Giga Means 1,000,000,000 | gigabyte (GB) | = | 1,000,000,000 Bytes |

At this point it would be good to point out why information stored in RAM is lost if the power goes off. Consider the way the following characters are translated into binary code for use by the computer.

| A | 01000001 |

|---|----------|

| В | 01000010 |

| C | 01000011 |

| X | 01011000 |

| Z | 01011010 |

| 1 | 00110001 |

| 2 | 00110010 |

Consider the column at the right, which represents how the computer stores information. Each of the 1's in the second column represents a circuit that is "on". If the power goes off, these circuits can NOT be "on" any more because the electricity has been turned off and any data represented by these circuits is lost

## **Central Processing Unit (CPU)**

The central processing unit is one of the two most important components of your microcomputer. It is the electronic brain of your computer. In addition to processing data, it controls the function of all the other components. The most popular microprocessors in IBM compatible computers are made by Intel. The generations of microprocessors are listed below.

| 1981 | 8088    |

|------|---------|

| 1984 | 80286   |

| 1987 | 80386   |

| 1990 | 80486   |

| 1993 | Pentium |

| 1996 | P-1     |

| 2002 | P-4     |

## **Output Devices**

Monitor Speakers

Printer Impact

Daisy Wheel

Dot Matrix

Non-Impact

Ink Jet

Laser

## Storage Devices

Floppy disk

Tape drive

Local drive (c)

Network drive (z)

CD-ROM

Zip disk

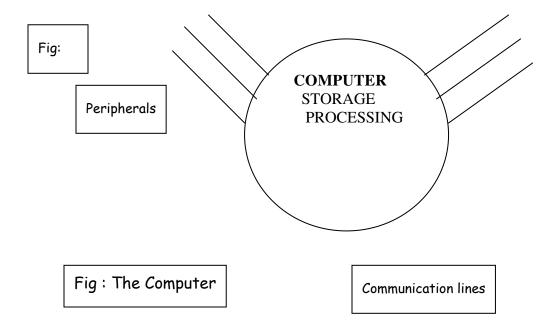

#### **Telecommunications**

Telecommunications means that you are communicating over long distances usually using phone lines. This enables you to send data to and receive data from another computer that can be located down the street, in another town, or in another country.

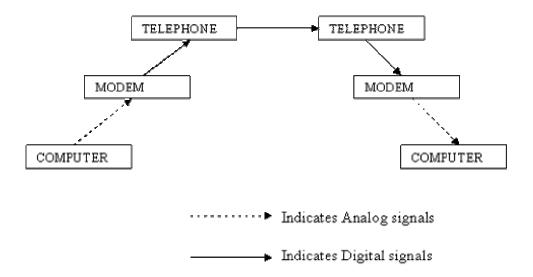

Telecommunications requires a communication device called a modem, which connects your computer to a standard phone jack. A modem converts the digital signals that your computer uses into analog signals that can be transmitted over the phone lines. To use a modem, you must also have communication software to handle the transmission process.

# **Computer Software**

#### **System Software**

System software will come provided with each computer and is necessary for the computer's operation. This software acts as an interpreter between the computer and user. It interprets your instructions into binary code and likewise interprets binary code into language the user can understand. In the past you may have used MS-DOS or Microsoft Disk Operating System which was a command line interface. This form of system software required specific commands to be typed. Windows 95 is a more recent version of system software and is known as a graphical interface. This means that it uses graphics or "icons" to represent various operations. You no longer have to memorize commands; you simply point to an icon and click.

#### **Program Software**

Program software is software used to write computer programs in specific computer languages.

## **Application Software**

Application software is any software used for specified applications such as:

- Word Processing

- Spreadsheet

- Database

- Presentation Graphics

- Communication

- Tutorials

- Entertainment, Games

## **Emerging Trends**

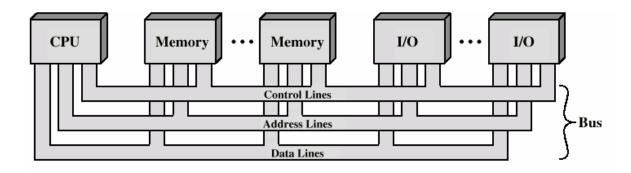

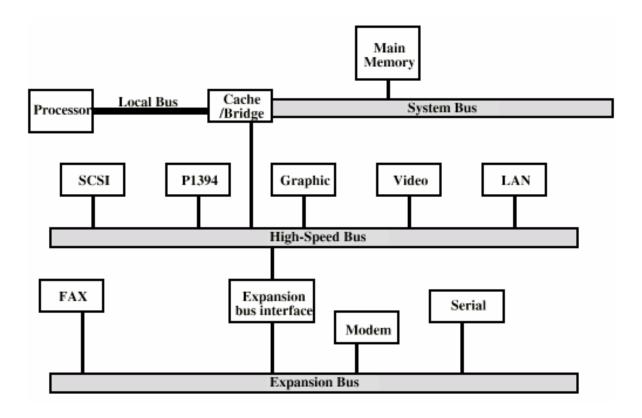

The components of a computer are connected by using buses. A bus is a collection of wire that carry electronic signals from one component to another. There are standard buses such as Industry Standard Architecture (ISA), Extended Industry Standard Architecture (EISA), Micro-Channel Architecture (MCA), and so on. The standard bus permits the user to purchase the components from different vendors and connect them easily.

The various input and output devices have a standard way of connecting to the CPU and Memory. These are called interface standards. Some popular interface standards are the RS-232C and Small Computer System Interconnect (SCSI). The places where the standard interfaces are provided are called ports.

#### **Data Representation**

#### Bits and Bytes

Data in Computers are represented using only two symbols '0' & '1'. These are called "Binary digiTS" (or) "**BITS**" for short. A set of 8 bits is called a **byte** and each byte stores one character. 2" Unique strings are represented using n bits only. For example, Using 2 bits we can represent 4=(2²) unique strings as 00, 01, 10, 11. ASCII (American Standards Code for Information Interchange) codes are used to represent each character. The ASCII code includes codes for English Letters (Both Capital & Small), decimal digits, 32 special characters and codes for a number of symbols used to control the operation of a computer which are non-printable.

### **Binary numbers**

Binary numbers are formed using the positional notation. Powers of 2 are used as weights in the binary number system. A binary number system. A binary number 10111, has a decimal value

equal to 1\*2<sup>4</sup>+0\*2<sup>3</sup>+1\*2<sup>1</sup>+1\*2<sup>0</sup>=23. A decimal number is converted into an equivalent binary number by dividing the number by 2 and storing the remainder as the least significant bit of the binary number. For example, consider the decimal number 23. Its equivalent binary number is obtained as show below in figure

## CONVERSION OF DECIMAL TO BINARY EXAMPLE. 23 = (0111)2

### **Hexadecimal Numbers**

High valued binary numbers will be represented by a long sequence of 0's and 1's. A more concise representation is using hexadecimal representation. The base of the hexadecimal system is 16 and the symbols used in this system are 0,1,2,4,5,6,7,8,9,A,B,C,D,E,F. Strings of 4 bits have an equivalent hexadecimal value. For example, **6B** is represented by 0110 1011 or 110 1011, **3E1** is represented by 0011 1110 0001 or 11 1110 0001 and **5DBE34** is represented by 101 1101 1011 1110 0011 0100. Decimal fractions can also be converted to binary fractions.

## **Parity Check Bit**

Errors may occur while recording and reading data and when data is transmitted from one unit to another unit in a computer Detection of a single error in the code for a character is possible by introducing an extra bit in its code. This bit, know as the **parity check bit**, is appended to the code. The user can set the parity bit either as even or odd. the user chooses this bit so that the total number of ones ('1') in the new code is **even** or **odd** depending upon the selection. If a single byte is incorrectly read or written or transmitted, then the error can be identified using the parity check bit.

## **Input Devices**

### **Key Board**

The most common input device is the Keyboard. It is used to input letters, numbers, and commands from the user.

#### Mouse

Mouse is a small device held in hand and pushed along a flat surface. It can move the cursor in any direction. In a mouse a small ball is kept inside and the ball touches the pad through a hole at the bottom of the mouse. When the mouse is moved, the ball rolls. This movement of the ball is converted into electronic signals and sent to the computer. Mouse is very popular in the modern computers that use Windows and other Graphical User Interface (GUI) applications.

### **Magnetic Ink Character Recognition (MICR)**

In this method, human readable characters are printed on documents such In this method, human readable characters are printed on documents such as cheque using special magnetic ink. The cheque can be read using a special input unit, which can recognize magnetic ink characters. This

method eliminates the need to manually enter data from cheques into a floppy. Besides saving time, this method ensures accuracy of data entry and improves security.

## **Optical Mark Reading and Recognition (OMR)**

In this method, special pre-printed forms are designed with boxes which can be marked with a dark pencil or ink. Such a document is read by a document reader, which transcribes the marks into electrical pulses which are transmitted to the computer. These documents are applicable in the areas where responses are one out of a small number of alternatives and the volume of data to be processed is large. For example:

- Objective type answer papers in examinations in which large number of candidates appear.

- Market surveys, population survey etc.,

- Order forms containing a small choice of items.

- Time sheets of factory employees in which start and stop times may be marked.

The advantage of this method is that information is entered at its source and no further transcription is required.

## **Optical Character Recognition (OCR)**

An optical scanner is a device used to read an image, convert it into a set of 0's and 1's and store it in the computer's memory. The image may be hand-written document, a typed or a printed document or a picture.

## **Bar Coding**

In this method, small bars of varying thickness and spacing are printed on packages, books, badges, tags etc., which are read by optical readers and converted to electrical pulses. The patterns of bars are unique an standardized. For example, each grocery product has been given unique 10-digit code and this is represented in bar code form on every container of this product.

## **Speech Input Unit**

A unit, which takes spoken words as its input, and converts them to a form that can be understood by a computer is called a speech input unit. By understanding we mean that the unit can uniquely code (as a sequence of bits) each spoken word, interpret the word and initiate action based on the word.

# **Output Devices**

## Monitor or Video Display Unit (VDU)

Monitors provide a visual display of data. It looks like a television. Monitors are of different types and have different display capabilities. These capabilities are determined by a special circuit called the Adapter card. Some popular adapter cards are,

- Color Graphics Adapter (CGA)

- Enhanced Graphics Adapter (EGA)

- Video Graphics Array (VGA)

- Super Video Graphics Array (SVGA)

### THE LECTURES IN A GO

- Defination Of computer

- History Of Computers

- Classification Of Computers

- Explanation about i/p and o/p devices

- Explanation about storage devices

- Types of computer software

# **Questions:**

- 1. When u switch on your computer which software you see first and what is the utility of that software.

- 2. Suppose on fine day you are working on ur computer and power goes off, again u switch on our computer, what type of booting is done by that computer.

- 3. Write the essential parts of ur computer system without which u cant work and also list that parts which are optional.

- 4. How many types of storage are normally there in storage unit of a computer system? Justify the need for each storage type. Explain them.

- 5. What are the basic components of the CPU of a computer systems? Describe the roles of each of the components in the functioning of a computer systems.

- 6. Suppose an entrance exam is held and thousands of students appeared in that exam, Which device u will use to evaluate the answer sheets and why?

- 7. Hardware and software are like two sides of a coin. Do you agree or disagree, Give reasons.

#### END OF TODAYS LECTURE...

#### **References:**

- COMPUTER FUNDAMENTALS

Pradeep .K.Sinha and Priti Sinha , BPB PUBLICATIONS

- 2. COMPUTER ORGANISATION AND ARCHITECTURE William Stallings Prentice PUBLICATIONS

# Lecture 2

## **GENERATIONS OF COMPUTERS**

## **Objectives of the lecture:**

1.To learn the generation of the computers.

Hello!friends, I am sure now you must be well versed with the History of computers from the previous lecture. Today I will be completing the remaining part of the previous lecture and then starting with the generations which tells how it has evolved from its early days, to become a powerful and useful tool for all types of users in today's society. So Lets start on..

#### Contd.

Lets start with the defination of Pixels, the smallest dot that can be displayed is called a pixel. The number of pixels that can be displayed vertically and horizontally gives the maximum resolution of the monitor. The resolution of the monitor determines the quality of the display. The higher the resolution the better is the quality of the display. Some popular resolution are 800\*640 pixels, 1024\*768 pixels, 1280\*1024 pixels.

#### **Printer**

## Line printer

- It prints a complete line at a time.

- Printing speed varies from 150 lines to 2500 lines per minute with 96 to 160 character on a 15-inch line.

- Six to eight lines per vertical inch are printed.

- Usually 64 and 96 character sets are used with English letters.

- Two types of Line Printers are available.

- **Drum Printers:** It consists of a cylindrical drum. The characters to be printed are embossed on its surface

- Chain Printers: I have a steel band on which the character sets are embossed.

#### **Serial Printers**

- It prints one character at a time, with the print head moving across a line.

- They are similar to typewriters.

- They are normally slow (30 to 300 character per second)

- The most popular serial printer is "Dot Matrix Printer".

- Her character to be printed is made up of a finite number of dots and so, the print head consists of an array of pins.

- Characters to be printed are sent one character at a time from the memory to the printer. The character code is decoded by the printer electronics and activates the appropriate pins in the print head.

- Many dot matrix printers are bi-directional. i.e. they print form left to right as well as from right to left on return. This enhances the speed of printing.

- The printing speed is around 300 characters per second.

## **Letter Quality Printers**

- Here the characters are represented by sharp continuous lines and so the output is good looking

- An example of such a printer is "Inkjet Printer".

- It consists of a print head, which has a number of small hole or nozzles.

- Individual holes can be heated very rapidly by an integrated circuit resistor. When the resistor heats up, the ink near it vaporizes and is ejected through the nozzle and makes a dot on paper placed near the head.

- A high-resolution inkjet printer has around 50 nozzles within a height of 7mm and can print with a resolution of 300 dots per inch.

- Latest inkjet printers have multiple heads, on per color, which allows color printing.

- The printing speed is around 120 characters per second.

#### **Laser Printers**

- Here an electronically controlled laser beam traces out the desired character to be printed

on a photoconductive drum. The drum attracts an ink toner on o the exposed areas. This

image is transferred to the paper, which comes in contact with the drum.

- Low speed laser printers, which can print 4 to 16 pages per minute, are now very popular and the unit cost is around Rs.0.5 lakh.

- Very fast printers print 10,000 lines per minute and cost per unit is around R.5 lakhs. These printers give excellent outputs and can print a variety of fonts.

- As these printers do not have type head striking on a ribbon, they are known as non-impact printers.

Apart from printers, the other output devices are given below:

- 1. Drum Plotter

- 2. Flat Bed Plotter

- 3. Microfilm and Microfiche

- 4. Graphic Display device (Digitizing Tablet)

- 5. Speech Output Unit

## **Computer Memory**

## **Main Memory**

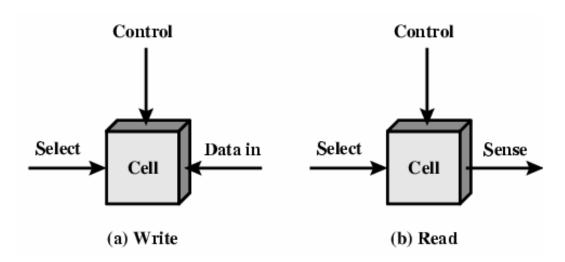

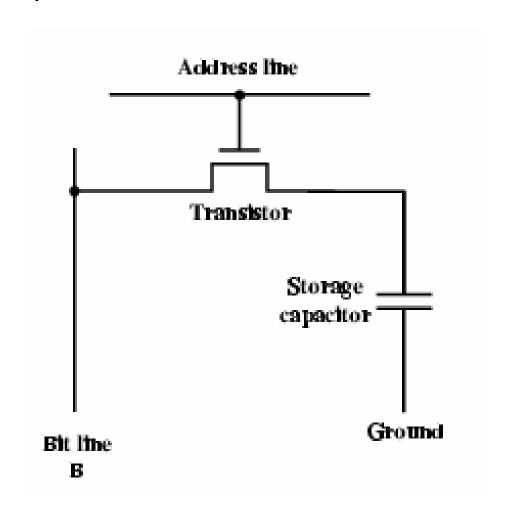

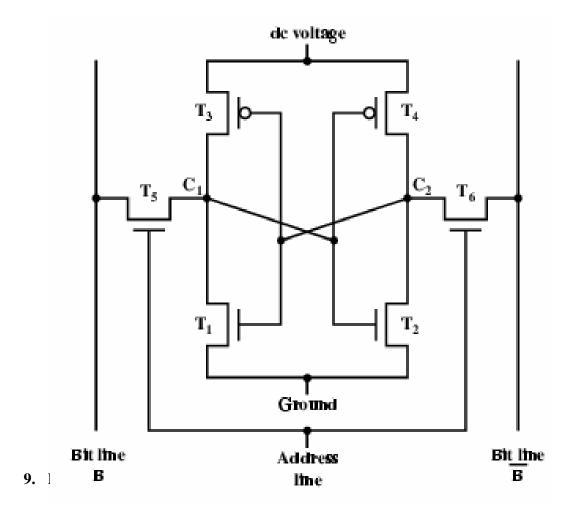

A **flip-flop** made of electronic semiconductor devices is used to fabricated a memory cell. These memory cells organized as a **Random Access Memory** (**RAM**). Each cell has a capability to store one bit of information. A main memory or store of a computer is organized using a large number of cells. Each cell stores a binary digit. A memory cell, which does not loose the bit stored in it when no power is supplied to the cell, is know as a **non-volatile cell**.

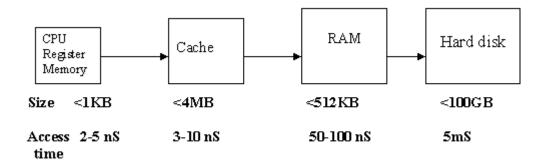

A word is a group of bits, which are stored and retrieved as a unit. A memory system is organized to store a number of words. A Byte consists of 8 bits. A word may store one or more bytes. The storage capacity of a memory is the number of bytes it can store. The address of the location from where a word is to be retrieved or to be stored is entered in a Memory Address Register (MAR). The data retrieved from memory or to be stored in memory are placed in a Memory Data Register (MDR). The time taken to write a word is known as the Write time. The time to retrieve information is called the Access time of the memory.

The time taken to access a word in a memory is independent of the address of the word and hence it is know as a **Random Access Memory** (**RAM**). The main memory used to store programs and data in a computer is a RAM. A RAM may be fabricated with permanently stored information, which cannot be erased. Such a memory is called a **Read Only Memory** (**ROM**). For more specialized uses, a user can store his won special functions or programs in a ROM. Such ROM's are called **Programmable ROM** (**PROM**). A serial access memory is organized by arranging memory cells in a linear sequence. Information is retrieved or stored in such a memory by using a read/write head. Data is presented serially for writing and is retrieved serially during read.

## Secondary or Auxiliary storage devices

Magnetic surface recording devices commonly used in computers are Hard disks, Floppy disks, CD-ROMs and Magnetic tapes. These devices are known as secondary or auxiliary storage devices. We will see some of these devices below.

## Floppy Disk Drive (FDD)

In this device, the medium used to record the data is called as floppy disk. It is a flexible circular disk of diameter 3.5 inches made of plastic coated with a magnetic material. This is housed in a square plastic jacket. Each floppy disk can store approximately on million characters. Data recorded on a floppy disk is read and stored in a computer's memory by a device called a floppy disk is read and stored in a computer's memory by a device called a floppy disk drive (FDD). A floppy disk is inserted in a slot of the FDD. The disk is rotated normally at 300 revolutions per minute. A reading head is positioned touching a track. A voltage is induced in a coil wound on the head when a magnetized spot moves below the head. The polarity of the induced voltage when a 0 is read. The voltage sensed by the head coil is amplified, converted to an appropriate signal and stored in computer's memory.

- Floppy Disks com with various capacities as mentioned below.

- $5^{1/4}$  drive- 360KB, 1.2MB (1 KB=  $2^{10}$  = 1024 bytes)

- $3^{1/2}$  drive- 1.44 Mb, 2.88 MB (1MB=  $2^{20}$  bytes)

## **Compact Disk Drive (CDD)**

CD-ROM (Compact Disk Read Only Memory) used a laser beam to record and read data along spiral tracks on a 5<sup>1/4</sup> disk. A disk can store around 650 MB of information. CD-ROMs are normally used to store massive text data. (such as encyclopedias) which is permanently recorded and read many times. Recently CD writers have come in the market. Using a CD writer, lot of information can be written on CD-ROM and stored for future reference.

#### Hard Disk Drive (HDD)

Unlike a floppy disk that is flexible and removable, the hard disk used in the PC is permanently fixed. The hard disk used in a higher end Pc can have a maximum storage capacity of 17 GB (Giga Byte; 1 GB= 1024 MB = 2<sup>50</sup> bytes). Now a days, hard disks capacities of 540 MB, 1 GB, 2 GB, 4 GB and 8 GB are quite common. The data transfer rate between the CPU and hard disk is much higher as compared to the between the CPU and the floppy disk drive. The CPU can use the hard disk to load programs and data as well as to store data. The hard disk is a very important Input/Output (I/O) device. The hard disk drive doesn't require any special care other than the requirement that one should operate the PC within a dust-free and cool room (preferably airconditioned).

In summary, a computer system is organized with a balanced configuration of different types of memories. The main memory (RAM) is used to store program being currently executed by the computer. Disks are used to store large data files and program files. Tapes are serial access memories and used to backup the files form the disk. CD-ROMs are used to store user manuals, large text, audio and video data.

## **Application and System Software**

#### Software & Hardware

A set of programs associated with the operation of a computer is called software. The electronic circuits used in building the computer that executes the software is known as the **hardware** of the computer. For example, a TV bought from a shop is hardware; the various entertainment programs transmitted from the TV station are software. An important point to note is, hardware is a one-time expense and is necessary whereas software is a continuing expense and is vital. Computer software may be classified into two broad categories:

## **Application Software**

It is the set of programs necessary to carry out operations for a specified application.

## Example

### **Programs**

- To solve a set of equations

- To process examination results

- To prepare a Pay-Bill for an organization

- To prepare Electricity-Bill for each month.

## **System Software**

These are general program written for the system, which provide the environment to facilitate writing of Application software. Some of the system programs are given below:

**Compiler:** It is a translator system program used to translate a High-level language program into a Machine language program.

**Assembler:** It is another translator program used to translate an Assembly language program into a Machine language program.

**Interpreter:** It is also a translator system program used to translate a High level language program into a Machine language program, but it translates and executes line by line.

**Loader:** It is a system program used to store the machine language program into the memory of the computer.

## **Computer Languages**

## Machine language

The computers can execute a program written using binary digits only. This type of programs is called machine language programs. Since these programs use only '0's and '1's it will be very difficult for developing programs for complex problem solving. Also it will be very difficult for a person to understand a machine language program written by another person. At present, computer users do not write programs using machine language. Also these programs written for execution in one computer cannot be used on another type of computer. i.e., the programs were machine dependent.

## **Assembly Language**

In assembly language **mnemonic** codes are used to develop program for problem solving. The program given below shows assembly language program to add two numbers A & B.

| Program code | <b>Description</b>              |

|--------------|---------------------------------|

| READ A       | It reads the value of A.        |

| ADD B        | The value of B is added with A. |

| STORE C      | The result is store in C.       |

| PRINT C      | The result in 'C' is printed.   |

| HALT         | Stop execution.                 |

Assembly language is designed mainly to replace each machine code with and understandable mnemonic code. To execute an assembly language program it should first be translates into an equivalent machine language program. Writing and understanding programs in assembly language is easier than that of machine language. The programs written in assembly language are also machine dependent.

## **High Level Languages**

High level language are developed to allow application programs, which are machine independent. High level language permits the user to use understandable codes using the language structure. In order to execute a high-level language program, it should be translated into a machine language either using a compiler or interpreter. The high level languages commonly used are **FORTRAN** (**FOR**mula **TRAN**slation), **BASIC** (**Beginner**'s **All-purpose Symbolic Instruction Code**), **COBOL** (**CO**mmon **B**usiness **O**riented **L**anguage). Recently developed programming language such as Visual Foxpro, Visual Basic (VB), Visual C++ (VC++) are more popular among the software developers. The following program written in BASIC language is to add two given numbers.

| Program Code | <b>Description</b>                      |

|--------------|-----------------------------------------|

| 10 INPUT A,B | To read the value of A&B                |

| 20 LET C=A+B | A&B are added and result is stored in C |

| 30 PRINT C   | Print the value of C                    |

| 40 END       | Stop execution                          |

# **Computers and Communications**

## Local Area Network (LAN) & Wide Area Network (WAN)

Computers available in remote locations can communicate with each other using a telecommunication line. One way of connecting the computers is by using devices called **modems**. A modem is used to transfer data from one computer to another using the telephone lines. A modem converts the strings of 0s and 1s into electrical signals which can be transferred over the telephone lines. Both the receiving and the transmitting computer have a telephone connection and a modem. An external modem is connected to the computer like a typical input or an output device. An internal modem is fitted into the circuitry related to the CPU and Memory.

Interconnection of computers which are within the same building or nearby locations forms a network of computers and this network is called a **Local Area Network (LAN)**. A LAN permits sharing of data files, computing resources and peripherals. Interconnection of computers located in far away locations using telecommunication system is known as **Wide Area Network (WAN)**.

#### COMPUTER COMMUNICATION USING TELEPHONE LINES

#### Internet

Intercommunication between computer networks is possible now. Computer networks located in different Organizations can communicate with each other through a facility know as Internet. Internet is a world wide computer network, which interconnects computer networks across countries. The Internet facilitates **electronic mail (email)**, **file-transfer** between any two computers and **remote access** to a computer connected in the internet. This intercommunication facility has changed the style of functioning of the business organization and it has made the world a global village.

So this covers the basics of computer system and its application. Now I would start with the generation of computers.

## First Generation Electronic Computers (1937-1953)

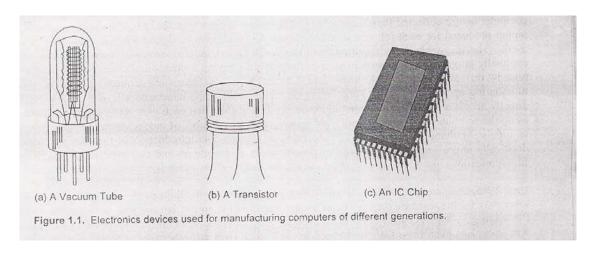

We have already discussed about some of the early computers –ENIAC , EDVAC , EDSAC , UNIVAC I , and IBM 701. These m/cs and others of their time were built by using thousands of vaccum tubes. A vaccum tube was fragile glass device which used filaments as a source of electronics and could control and amplify electronic signals. It was the only high speed electronic switching device available in those days. These vacuum tube computers could perform computations in milliseconds, and were referred to as first generation computers.

Memory was constructed using electromagnetic relays, and all data and instructions were fed into the system from punched cards. The instruction were written in m/c and assembly languages because high level programming languages were introduced much later.

### **Characteristic Features Of First Generation**

- 1. They were the fastest calculating device of their time

- 2. They were to bulky in their size, requiring large rooms for installation

- 3. 1000's of vacuum tubes which were used emitted large amount of heat and burnt out frequently. Hence the rooms / areas in which these computers were located had to be properly air conditioned.

- 4. Each vacuum tube consumed about half watt of power. Since a computer typically used more than ten thousand vacuum tubes the power consumption of these computers was very high.

- 5. As vacuum tubes used filaments, they had a limited life .Since thousand of vacuum tubes were used in making one computer these computers were prone to frequent hardware failures.

- 6. Due to low mean time failures, these computers required almost constant maintenance.

- 7. Thousands of individual components had to be assembled manually by hand into functioning ccts. Hence commercial production of these computers was difficult and costly.

- 8. Since these computers were difficult to program and use they had limited commercial use.

# Second Generation (1955-1964)

The second generation saw several important developments at all levels of computer system design, from the technology used to build the basic circuits to the programming languages used to write scientific applications.

Electronic switches in this era were based on discrete diode and transistor technology with a switching time of approximately 0.3 microseconds. The first machines to be built with this technology include TRADIC at Bell Laboratories in 1954 and TX-0 at MIT's Lincoln Laboratory.

Transistors soon proved to be better electronic switching devices than vacuum tubes, due to their following properties.

- 1. They were more rugged and easy to handle than tubes, since they were made of germanium semiconductor material rather than glass.

- 2. They were highly reliable as compared to tubes, since they had no part like a filament, which could burn out.

- 3. They could switch much faster than tubes.

- 4. They consumed almost  $1/10^{th}$  the power consumed by a tube.

- 5. They were much smaller than a tube.

- 6. They were less expensive to produce.

- 7. They dissipated much less heat as compared to vacuum tubes.

Due to the properties listed above second generation computers were more powerful, more reliable, less expensive, smaller, and cooler to operate than the first –generation computers.

**Memory**: is composed of the magnetic cores. Magnetic disk and magnetic tape were main secondary storage media used in secondary generation computers. Punched cards were still popular and widely used for preparing programs.

During this second generation many high level programming languages were introduced, including FORTRAN (1956), ALGOL (1958), and COBOL (1959). Important commercial machines of this era include the IBM 704, the 709 and 7094. The latter introduced I/O processors for better throughput between I/O devices and main memory.

### **Features Of Second Generation:**

- 1. They were more than ten times faster than the first generation computers.

- 2. They were much smaller than first generation computers, requiring smaller spaces.

- 3. Although the heat dissipation was much less than first generation computers, the rooms/areas in which the second generation computers were located had to be properly air conditioned.

- 4. They consumed much less power than the first generation computers.

- 5. They were more reliable and less prone to hardware failures than the first generation computers.

- 6. They had faster and larger primary and secondary storage as compared to first generation computers.

- 7. They were much easier to program and use than the first generation computers. Hence they had wider commercial use.

8. In these computers, thousands of individual transistors had to be assembled manually by hand into functioning ccts. Hence commercial production of these computers was difficult and costly.

Fig Electronics devices used for manufacturing computers of different generations

| ~ *** | Dec.         |      | ****      | vui  |     |      |

|-------|--------------|------|-----------|------|-----|------|

| 100   | PE (0.654) 1 | 1000 | F-4-77-00 | W-NA | 200 | 5000 |

|       |              |      |           |      |     |      |

| Generation<br>(Period) | Key hardware<br>Technologies                                                                                                                                                                                                                     | Key software<br>technologies                                                                                                                                                   | Key<br>characteristics                                                                                                                                                                                                                 | Some representative<br>systems                                                       |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| First (1942-1955)      | Vacuum tubes; electromagnetic relay<br>memory; punched cards secondary<br>storage                                                                                                                                                                | Machine and assembly languages;<br>stored program concept; mostly<br>scientific applications                                                                                   | Bulky in size; highly unreliable; limited<br>commercial use; commercial production<br>difficult and costly; difficult to use                                                                                                           | ENIAC, EDVAC,<br>EDSAC, UNIVAC. I,<br>IBM 701                                        |

| Second<br>(1955-1964)  | Transistors; magnetic cores memory;<br>magnetic tapes and disks secondary<br>storage                                                                                                                                                             | Batch operating system; high-level programming languages; scientific and commercial applications                                                                               | Faster, smaller, more reliable and easier to program than previous generation systems; commercial production was still difficult and costly                                                                                            | Honeywell 400, IBM<br>7030, CDC 1604,<br>UNIVACLARC                                  |

| Third<br>(1964-1975)   | ICs with SSI and MSI technologies;<br>larger magnetic cores memory; larger<br>capacity disks and magnetic tapes<br>secondary storage; minicomputers                                                                                              | Timesharing operating system; standardization of high-level programming languages; unbundling of software from hardware                                                        | Faster, smaller, more reliable, easier and cheaper to produce commercially, easier to use, and easier to upgrade than previous generation systems, scientific, commercial and interactive on-line applications                         | IBM 360/370, PDP-8, PDP-11, CDC 6600                                                 |

| Fourth (1975-1989)     | ICs with VLSI technology; microprocessors; semiconductor memory; larger capacity hard disks as in-built secondary storage; magnetic tapes and floppy disks as portable storage media; personal computers; spread of high-speed computer networks | Operating systems for PCs; GUI; multiple windows on a single terminal screen; UNIX operating system; C programming language; PC-based applications; network-based applications | Small, affordable, reliable, and easy to<br>use PCs; more powerful and reliable<br>mainframe systems; totally general<br>purpose machines; easier to produce<br>commercially                                                           | IBM PC and its clones, Apple II, TRS-80, VAX 9000, CRAY-1, CRAY-2, CRAY-XMP          |

| (1989-Present)         | ICs with ULSI technology; larger capacity main memory; larger capacity hard disks; optical disks as portable read-only storage media; notebook computers; powerful desktop PCs and workstations; very powerful mainframes; internet              | World Wide Web; multimedia applications; internet-based applications                                                                                                           | Portable computers; more powerful, cheaper, reliable, and easier to use desktop machines; very powerful mainframes; very high uptime due to hot-pluggable components; totally general purpose machines; easier to produce commercially | IBM notebooks, Pentium PCs, SUN Workstations, IBM SP/2, SGI Origin 2000, PARAM 10000 |

Figure 1.2. Computer generations – A summary.

## Summary of the Generation Of the Computers

### THE LECTURE IN A GO !!!!!!!!!!!!

- All computer systems perform the following 5 basic operations for converting raw input data into useful information- inputing, storing, processing, outputting, controlling.

- The input unit allows data and instruction to be fed from the outside world in computer acceptable form.

- The input interface transforms the data and instruction to be fed to the computer, through its input devices, into the binary codes, which are acceptable to the computer.

- The output unit allows the computer system to supply the information, obtained from data processing, to the outside world, in human acceptable(readable)from.

- The output interfaces transform the information, obtained from data processing, from binary form to human acceptable (readable) form.

- The storage unit of a computer system holds the data and instruction to be processed, and the intermediate and final results of processing. The 2 types of storage are Primary and Secondary storage. As compared to primary storage, secondary storage is slower in operation, larger in capacity, cheaper in price, and can retain information even when the computer system is switched off or reset.

- Different types of storage devices.

- During data processing, the actual execution of the instruction takes place in the Arithmetic Logic Unit(ALU) of a computer systems.

- The control unit of a computer system manages and co-ordinates the operations of all the other components the computer systems.

- The Control unit and the arithmetic unit Logic Unit of a computer system are jointly known as the Central Processing Unit(CPU), which serves as the brain of the computer system and is responsible for controlling the operations of all other units of the system.

- A computer is often referred to as computer system, because it is made up of integrated compinents(i/o, storage, CPU), which work together to perform the steps called for, in the program being executed.

- Different type of storage devices

- Modes of communication of data.

Yes with this we finish the introduction part of the computers. Now lets begin with the generations.

## **Emerging Trends**

### A new kid of device

The biggest immediate potential for this technology would be what could be dubbed a PDN - a personal digital notebook. Unlike the much ballyhooed Tablet PC (basically a Windows laptop with touch screen and handwriting recognition), such a device would expand the Palm paradigm: simple, immediately useful and usable, with a minimal OS. Not a replacement for a laptop, but a device which allows basic management functions with note taking and document display. There are a few simple reasons for this analysis: electronic ink will, at least initially, be monochrome,

and therefore appeal for usages which don't require color in real life, such as note taking, reading, managing your date-book and so on. (It is unlikely that Windows users will settle for a monochrome version of their OS without feeling they are losing something important.)

The phenomenal success of the Palm has shown that there is a market for handheld devices which don't try to rival with a complete computer. This notion could be expanded considerably, especially if the device is light and simple enough to allow for intuitive use even for a computer novice.

And then there is price, of course. One of the problems with Microsoft's conception of the Tablet PC is that it is a complete laptop - and it will come at prices of high-end portable computers, which it will only partly replace (at least initially). In order to be a genuinely useful complement to current devices, a true digital notebook would have to be both less complex and less expensive.

#### The role of electronic paper

In any case, electronic paper will play an important role in the development of next generation handheld devices: low power consumption, high contrast, a high resolution display which stays in place when a device is turned off and can be viewed in broad daylight, all these factors indicate that this technology will have a considerable impact on the devices we will find on the market.

This is not going to happen overnight, however. Until the best use for this technology potential is found, electronic ink displays will find their way into a number of existing platforms, such as next generation Palms or Pocket PCs.

The ultimate question is of course what the right mix of features will be: Digital Notebooks with built-in web-browsers? Course books with annotation and word-processing functions? Date books with handwriting recognition and built-in e-book readers, web browsers and GPS devices? It will take some time to sort this out - but there is a lot to be invented here...

# Question:

- 1. Hardware is one time expense but software is continuing expense. Discuss

- 2. You need to connect various computer systems in your college, what type of network you will establish and why. Justify your answer.

- 3. Can our systems work without RAM, Give reasons in support of your answer?

- 4. How does a normal user interact with the hardware of a computer system. Describe the various in between layers.

- 5. How can a business organization benefit through the use of internet.

## END OF TODAYS LECTURE...

### **REFERENCES:**

- 1. COMPUTER FUNDAMENTALS

- PRADEEP .K.SINHA BPB PUBLICATIONS

- 2. COMPUTER ORGANISATION AND ARCHITECTURE WILLIAM STALLINGS

# Lecture 3

## Contd.....

Hello! Friends, I am going to continue with the remaining generations of the computer. Now let us study about the third generation.

## **Third Generation (1964-1975)**

The third generation brought huge gains in computational power. Innovations in this era include the use of integrated circuits, or ICs (semiconductor devices with several transistors built into one physical component), semiconductor memories starting to be used instead of magnetic cores, microprogramming as a technique for efficiently designing complex processors, the coming of age of pipelining and other forms of parallel processing (described in detail in Chapter CA), and the introduction of operating systems and time-sharing.

The first ICs were based on small-scale integration (SSI) circuits, which had around 10 devices per circuit (or "chip"), and evolved to the use of medium-scale integrated (MSI) circuits, which had up to 100 devices per chip.

Multilayered printed circuits were developed and core memory was replaced by faster, solid state memories. Computer designers began to take advantage of parallelism by using multiple functional units, overlapping CPU and I/O operations, and pipelining (internal parallelism) in both the instruction stream and the data stream.

In 1964, Seymour Cray developed the CDC 6600, which was the first architecture to use functional parallelism. By using 10 separate functional units that could operate simultaneously and 32 independent memory banks, the CDC 6600 was able to attain a computation rate of 1 million floating point operations per second (1 Mflops).

Five years later CDC released the 7600, also developed by Seymour Cray. The CDC 7600, with its pipelined functional units, is considered to be the first vector processor and was capable of executing at 10 Mflops. The IBM 360/91, released during the same period, was roughly twice as fast as the CDC 660. It employed instruction look ahead, separate floating point and integer functional units and pipelined instruction stream.

The IBM 360-195 was comparable to the CDC 7600, deriving much of its performance from a very fast cache memory. The SOLOMON computer, developed by Westinghouse Corporation, and the ILLIAC IV, jointly developed by Burroughs, the Department of Defense and the University of Illinois, were representative of the first parallel computers. The Texas Instrument Advanced Scientific Computer (TI-ASC) and the STAR-100 of CDC were pipelined vector processors that demonstrated the viability of that design and set the standards for subsequent vector processors.

## Features of Third Generation Computers are as follows:

- 1. They were much more powerful than the second generation computers. They were capable of performing about 1 million instruction per second.

- 2. They were much smaller than second generation computers, requiring smaller space

- 3. Although the heat dissipation was much less than second generation computers, the room in which the third generation were kept had tyo be properly air conditioned.

- 4. They consumed much less power.

- 5. They were more reliable and less prone to hardware failures than the second generation computers. Maintenance cost was much lower.

- 6. They had faster and larger primary and secondary storage as compared to second generation computers.

- 7. They were totally general purpose m/c.

- 8. Their manufacturining did not require manual assembly of individual components into electronic ccts, resulting in reduced human labor and cost involved at assembly stage. Commmercial production of this system were easier and cheaper.

- 9. Time sharing OS allowed interactive usage and simultaneous use of these systems by a larger number of users.

- 10. Time sharing OS made On Line systems feasible, resulting in the usage of these systems for new on-Line applications.

- 11. The minicomputers of the third generation made computers affordable even by smaller companies.

# Fourth Generation (1975-1989)

The next generation of computer systems saw the use of large scale integration (LSI - 1000 devices per chip) and very large scale integration (VLSI - 100,000 devices per chip) in the construction of computing elements. At this scale entire processors will fit onto a single chip, and for simple systems the entire computer (processor, main memory, and I/O controllers) can fit on one chip. Gate delays dropped to about 1ns per gate.

Semiconductor memories replaced core memories as the main memory in most systems; until this time the use of semiconductor memory in most systems was limited to registers and cache. During this period, high speed vector processors, such as the CRAY 1, CRAY X-MP and CYBER 205 dominated the high performance computing scene. Computers with large main memory, such as the CRAY 2, began to emerge. A variety of parallel architectures began to appear; however, during this period the parallel computing efforts were of a mostly experimental nature and most computational science was carried out on vector processors. Microcomputers and workstations were introduced and saw wide use as alternatives to time-shared mainframe computers. It started a new social revolution the Personal computer revolution. Overnight,

computers became incredibly compact. They became inexpensive to make, suddenly it became possible for anyone to own a computer.

During this generation magnetic core memories were replaced by semiconductor memories, resulting in large random access memories with very fast access time. Hard Disk became cheaper, smaller and large in capacity. In addition to magnetic tapes, floppy disks became very popular as a portable medium for porting programs and data from one computer system to another.

Another feature introduced was high speed computer networking, which enabled multiple computer to be connected together .To enable to communicate with each other Local Area Networks Became Popular. During this generation UNIX operating system and C programming became popular.

## **Features Of Fourth Generation computers**

- 1. The PC's were smaller and cheaper than Main Frame or Minicomputers of third generation

- 2. Mainframes were much more powerful.

- 3. No Air conditioning were required for the PC's

- 4. They consumed much less power than the third generation computers

- 5. They were more reliable and less prone to the hardware failures, hence the maintanence cost was negligible

- 6. They had faster and much larger secondary and primary storage.

- 7. Graphical user interface (GUI) enabled new users to quickly learn how to use computers.

- 8. Network of computers enabled sharing of resources like disks, printers, among multiple computers and their users.

- 9. These systems also used add-on hardware feature.

- 10. They made computers affordable even by individuals for their personal use at home.

# Fifth Generation (1989)

During this generation the VLSI technologies became ULSI (Ultra Large scale Integration). Storage technologies also advanced very fast, making larger and larger main memory and disk storage available in newly introduced systems. During the fifth generation optical disks also emerged as a popoular portable mass storage media. They are more commonly known as CD-ROM(Compact Disk-Read Only Memory) because they are mainly used for storing programs and data, which are only read(not written/modified)

## Characteristic Features Of Fifth generation computers are as follows

- 1. Portable PCs are much more smaller and handy than PCs of the fourth generation, allowing users to use computing facility even while traveling.

- 2. The desktop PCs and workstations are several times more powerful than the PCs of fourth generation.

- 3. The mainframes are several times more powerful than the mainframes systems of the fourth generation.

- 4. They consume much less power than the predecessors.

- 5. They are more reliable and less prone to the hardware failures than their predecessors. Hence the maintenance cost is negligible

- 6. They have faster and larger primary and secondary storage

- 7. They are totally general purpose m/c

- 8. More user friendly

- 9. These systems also use the concept of unbundled software and add-on hardware, allowing the users to invest only in the hardware configuration and software of their need and value.

### THE LECTURES IN A GO |||||||||||

- 1. Important points of the Third Genrations.

- 2. Important points of the fourth and fifth generations.

END OF TODAYS LECTURE.....

# **REFERENCES:**

1. COMPUTER FUNDAMENTALS

RADEEP .K.SINHA BPB PUBLICATIONS

2. COMPUTER ORGANISATION AND ARCHITECTURE

WILLIAM STALLINGS PRENTICE PUBLICATIONS

# Lecture 4

# **CLASSIFICATION OF COMPUTERS**

### **Objectives of the lecture:**

1.To understand the Classification Of Computers

Hello students, I am sure you all must be well versed with the generations of the computer from my previous lectures and I am sure you want to know more about it. So let us begin todays session with the defination of the computer and then I will explain the characteristics, its types and so on..

<u>Defination:</u> It's a device which can operate on the data. Data could be anything like bio-data, marks obtained ,airline or railway reservations, or in use of solving scientific research problems. A computer can store, process, and retrive data as and when desired.

One can even call, it as Data Processor because it processes data. Thus in short we can define it as the activity of processing data using a computer is called **Data Processing**. Gather data from various incoming sources, merge them in desired order, and finally print them in the desired format.

## Activities involved in Data Processing are:-

- 1. Capturing the input data.

- 2. Manipulating the data

- 3. Managing the output results.

#### CHARACTERISTIC OF COMPUTERS

#### 1. Automatic:

Computers are automatic m/c because once started on a job they carry on until the job is finished ie it works from a program a program of coded informations which specify how exactly a particular job is done

### 2. Speed:

It is a very fast device. It can perform in a few seconds ie a compouter does in 1 min. what would take a man his entire life. While talking about speed we mean speed in microseconds 10 to the power of -6, the nano seconds ie 10 to the power of-9, and even

picoseconds ie 10 to the power of -12.Powerful computer performs several billion ie 10 to the power 9 simple arithmetic expressions.

## 3. Accurracy:

Computers are very accurate. The accuracy of computer is very high , and the degree of accuracy depends upon its design.

### 4. Diligence:

Unlike human being a computer is free from monotony, tiredness and lack of concentration. It can work for hours without creating any errors and without grumbling.

### 5. Versatility:

It is the most important thing about a computer. One moment it is preparing a result of an examination , the next it is busy preparing bills, in between it may be helping an office secretary to trace an important letter in seconds. Briefly the computer is capable of performing any task .

## 6. Power of Remembering

A computer can store and recall any amount of information because of its secondary storage capability. Even aftewr several years the information recalled would be as accurate as on the day when it was fed.

#### 7. No. I.Q:

The computer possess no intelligence of its own. Its I.Q is zero. at leat until today. It has to be told what to do and in what sequence.

## 8. No Feeling:

Computers are devied of emotions. They have no feelings and no instinct because they are m/c, their judgement is based on the instructions given to them in the form of programs that are written by us.

### **EVOLUTION OF COMPUTERS**

Let us discuss the history of the computers, the first mechanical adding m/c was invented by Blaise Pascal in 1642.Later in the year 1671,Baron Gottfried Wilhelm von Leibniz of germany invented the first calculator for multiplication. Herman Hollerith came up with the concept of punchedcards, which are extensively used as input medium in computers.

Business m/c and calculators made their appearance in Europe and America towards end of 19 th centuray.

Charles Babbage a 19 th century Professor at Cambridge University , is considered the father of modern digital computers. Babbage had to spend several hours checking these tables which made his job difficult , as a result he started to build a m/c , which could compute tables guaranteed to

be error free. In 1822 he designed a "Difference Engine" which produce reliable tables. And in 1842 Babbage came out with his idea of analytical engine.

Let us now briefly discuss about some of well known early computers:-

## 1. The Mark I Computer:

Known as **Automatic Sequence Controlled Calculator**, this was the first fully Automatic calculating m/c designed by Howard a. Aiken of Harvard University, in collaboration with IBM .It was based on the concept of punched cards. Although it was very complex in design and huge in size .It used 3000 electrically actuated switches to control its operations and was approx, 50 feet long and 8 feet high.

## 2. Atans off – Berry Computer:

This was developed by Dr.John Atansoff to solve mathematical equation. I t was called ABC computers. It used 45 vacuum tubes for internal logic and capacitors for storage

- **3.** The ENIAC (1943-46): This is the first Electronic Numerical Integrator and Computer designed and constructed under the supervision of John Mauchly and John Presper Eckert at the university of Pennsylvania, was the worlds first general purposeelectronic digital computer. This project was a response to U.S. wartime needs The Army's Ballistics Research Laboratory(BRL), an agency responsible for developing range trajectory tables for new wepons, was having difficulty supplying these tables accurately and within a reasonable time frame. The BRL employed more than 200 people, mostly women who using desktop calculators, solved the necessary balastic equations. Preparation of the tables for a single weapon would take one person many hours, even days.

- **4. Mauchly,** a professor of electrical engineering at the university and Eckert one of this graduate students, proposed to build general purpose computer using vacuum tubes to be used for the BRL's application. The resulting m/c was enormous weighing 30 tones, occupying 15,000 square feet, having more than 18,000 vacuum tubes it consumed 140 kilowatts of power. It was also faster than any electromechanical computer, being capable of 5000 additions per second.

- **5. The EDVAC** (**1946-52**): (Electronic Discrete Variable Automatic Computer)A major drawback of ENIAC was that its programs were wired on boards which made it difficult to change the programs. This problem was later over commed by Dr. John Neumann. Basic idea behind this concept was that the sequence of instruction and the data can be stored in the memory of the computer.

### **VON NEUMANN MACHINE**

As mentioned above the task of entering and altering programs for ENIAC was extremely tedious. The programming process could be facilitated if the programs could be represented in the form suitable for storing in memory alongside the data. Then a computer could get its instruction by reading them from memory and a program could be set or altered by setting the values of a portion of memory. This idea known as stored program concept is usually attributed to ENIAC designers, most notably the mathematician John Von Neumann, who was the consultant on the ENIAC project. The first publication of the idea was in 1945 proposal by von Neumann for a new computer, the EDVAC (Electronic Discrete Variable Computer) Von Neumann and his colleagues began the design of new stored program computer, referred to as the IAS computer,

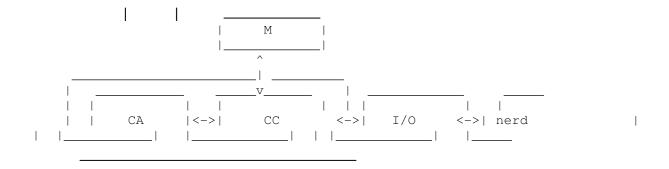

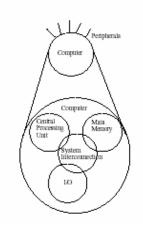

#### General Structure of the IAS computer.

- A main memory which stores data and instructions

- An arithmetic and logical unit(ALU) capable of operating on binary data.

- A control unit, which interprets the instruction in memory and causes them to be executed.

- Input and Output(I/O) equipment operated by control unit.

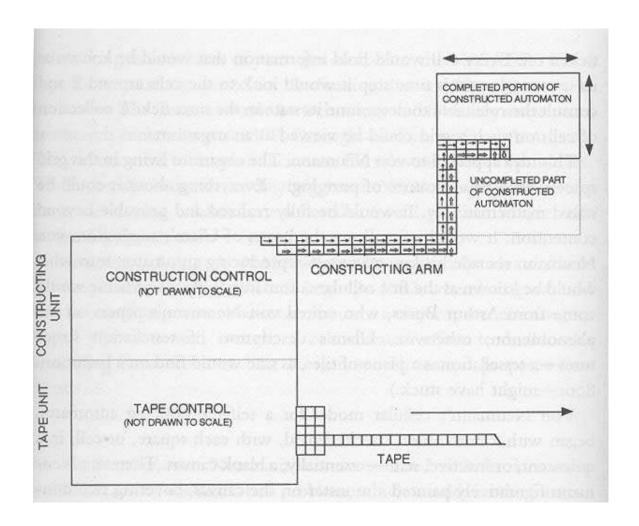

Fig 1 Structure Of the IAS Computer

### Explanation of the above:

- Since the device is primarily a computer it will have to perform the elementary operations of arithmetic most frequently. These addition, subtraction, multiplication and divisions: +,-,x,\.are taken care by central arithmetical part of the device. ie CA

- The Logical control of the device that is the proper sequencing of its operations, is most efficiently carried by a central control organ ie CC

- Any device which is to carry out long and complicated sequences of operations must have a considerable memory, ie M

- The above three specific parts CA, CCie(C),M constitute the input and output devices.

- The devices must be endowed with the ability to maintain input and output contact with some specific medium of this type. The medium will be called the outside recording medium of the device :R

- The device must have some organ to transfer information from R into its specific parts C and M. ie I

- The device must have some organ to transfer from C, M into R. ie O.

All of todays computers have this same general structure and function and are therefore referred to as Von Neumann m/c.

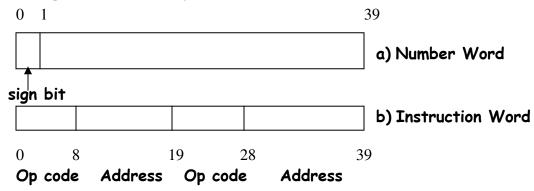

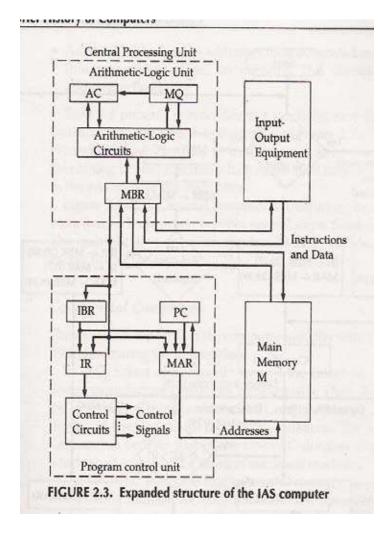

## Following is the IAS memory formats

Fig Expanded structure of the IAS computer

According to the above fig.

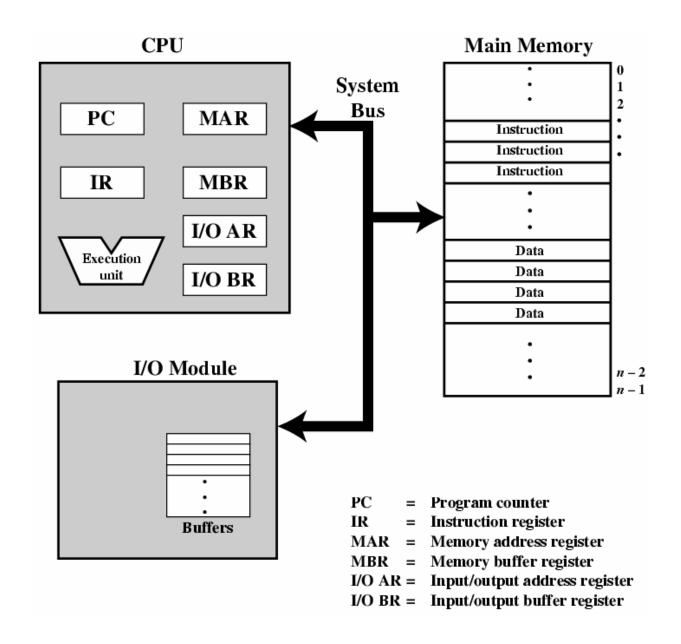

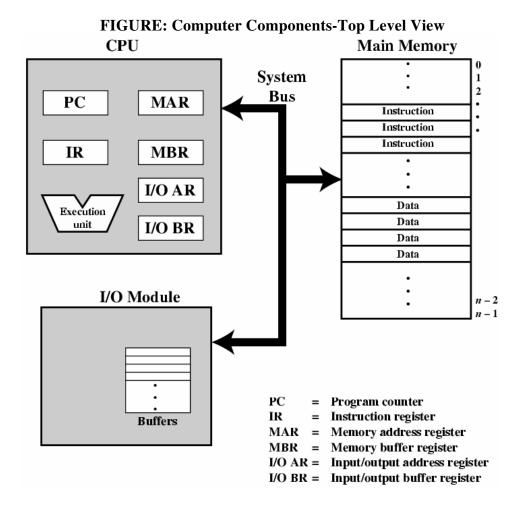

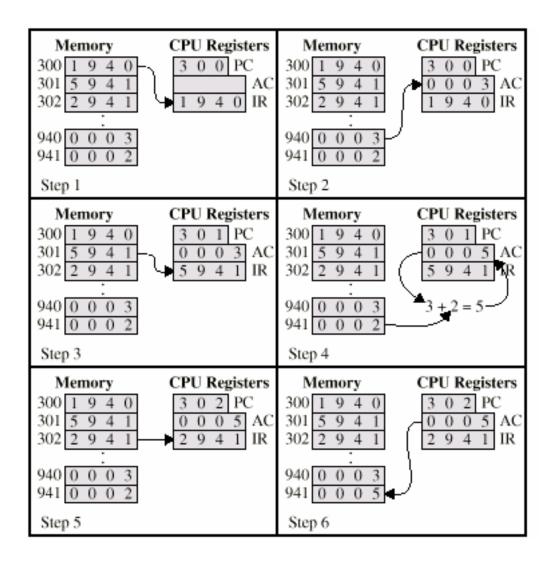

- (MBR) Memory Buffer Register: Contains the word to be stored in memory, or is used to receive a word from memory.

- (MAR) Memory Address Register: Specifies the address in the memory of the word to be written from or read into the MBR.

- (IR)Instruction register: Contains the 8 bit opcode instruction being executed

- (IBR)Instruction Buffer Register: Employed to temporartily hold the right –hand instruction from a word in memory.

- (PC)Program counter: Contains the address of the next instruction-pair to be fetched from memory.

- (AC)Accumulator and Multiplier-Quotient(MQ):Employed to temporarily hold operands and results of ALU operations. For eg. The result of multiplying two 40-bit numbers is an 80-bit number; the most significant 40 bits are stored in AC and the least significant in the MQ.

- **6.** The EDSAC(1947 49) (Electronic delay storage automatic Calculator. This m/c was developed by a group of scientest headed by the professor Maurice Wilkes. In this m/c addition operation was accomplished in 1500 microseconds and multiplication operation in 4000 microseconds.

- **7. UNIVAC(1951)**: It's a Universal Automatic Computer was the first digital computer, which was not "one of the kind". The first Was installed and used continuously for 10 yrs. In 1952 the international Business m/c corp.introduced the 701 commercial computer..

#### **Emerging Trends**

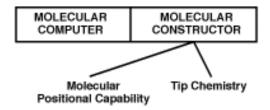

The study of artificial self replicating systems was first pursued by <u>von Neumann</u> in the 1940's. Subsequent work, including <u>a study by NASA in 1980</u>, confirmed and extended the basic insights of von Neumann. More recent work by <u>Drexler</u> continued this trend and applied the concepts to molecular scale systems

## Drexler's architecture for an assembler

Drexler's assembler follows the Von Neumann architecture, but is specialized for dealing with systems made of atoms. The essential components in Drexler's Assembler are shown in figure 2. The emphasis here (in contrast to von Neumann's proposal) is on small size. The computer and constructor both shrink to the molecular scale, while the constructor takes on additional detail consistent with the desire to manipulate molecular structures with atomic precision. The molecular constructor has two major subsystems: (1) a positional capability and (2) the "tip chemistry."

# Drexler's Architecture for an Assembler

Figure 2.

The positional capability might be provided by one or more small robotic arms, or alternatively might be provided by any one of a wide range of devices that provide positional control[14]. The emphasis, though, is on a positional device that is very small in scale: perhaps 0.1 microns (100 nanometers) or so in size.

As an aside, current SPM (Scanning Probe Microscope) designs employ piezoelectric elements for positional control[21]. A rather obvious question to ask is: why prefer mechanical positioning systems over piezoelectric or other electrostatic devices? The reasons for using basically mechanical devices at the molecular scale are similar to the reasons that mechanical devices are employed at the macroscopic scale: the desire for compactness and high positional accuracy (e.g., high stiffness). This weighs against electrostatic and piezoelectric devices. Molecular mechanical devices, on the other hand, can employ very stiff materials and, with appropriate design, can have joints that can rotate easily but which at the same time provide high stiffness in other degrees of freedom [1,20]

The "tip chemistry" is logically similar to the ability of the Von Neumann Universal Constructor to alter the state of a cell at the tip of the arm, but here the change in "state" must correspond to a real world change in molecular structure. That is, we must specify a set of well defined chemical reactions that take place at the tip of the arm, and this well defined set of chemical reactions must be sufficient to allow the synthesis of the class of structures of interest.

The assembler, as defined here, is not a specific device but is instead a class of devices. Specific members of this class will deal with specific issues in specific ways.

### THE LECTURE IN A GO

- 1. A computer is normally considered to be a calculating device, which can perform arithmetic at enormous speed. It is also known as a data processor since it not only computes in a usual sense, but also performs other functions with the data.

- 2. The activity of processing data using a computer is called data processing. Data is the raw material used as input to data processing, and information is processed data obtained as the output of data processing.

- 3. Computers are characterized by their being automatic, speed and accuracy of computing, diligence, versatility, power of remembering and lack of intelligence and feelings.

- 4. Charles Babbage is considered the father of modern digital computers.

- 5. Some of the well known early computers are the Mark1, Atanasoft-Berry, the ENIAC, the EDSAC, the UNIVAC 1.

- 6. Dr. John Von Neumann introduced the "stored program" concept which considerably influenced the development of modern digital computers. Due to this features we often refer to modern digital computers as stored program digital computers.

END OF TODAYS LECTURE.....

## **REFERENCES:**

- COMPUTER FUNDAMENTALS

PRADEEP .K.SINHA BPB PUBLICATIONS

- 2. COMPUTER ORGANISATION AND ARCHITECTURE WILLIAM STALLINGS PRENTICE HALL OF INDIA

## Lecture 5

## ORGANISATION / STRUCTURE /FUNCTION

### **Objectives of the lecture:**

1.To understand the Organisation / Structure /Function

Hello! students, today we will learn about the structure and function of computers. which will help you to know about about CPU, Registers, Control Unit, ALU, along with this about the performance factors.

The intent of this lecture is to provide a discussion of the fundamentals of computer organization, structure and function .

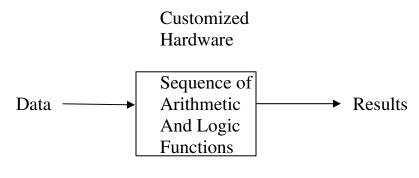

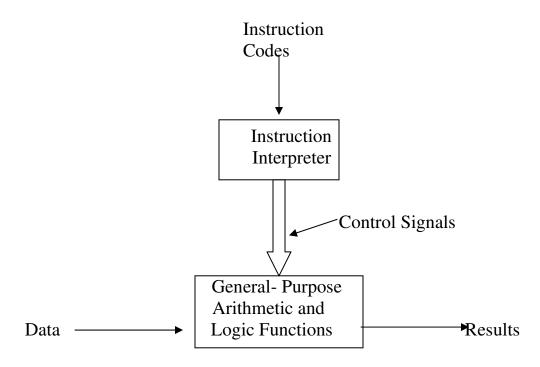

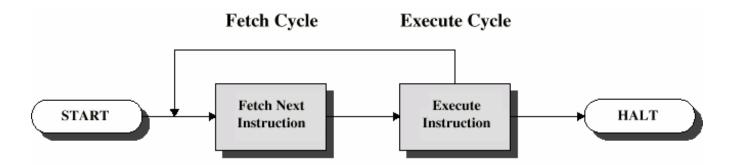

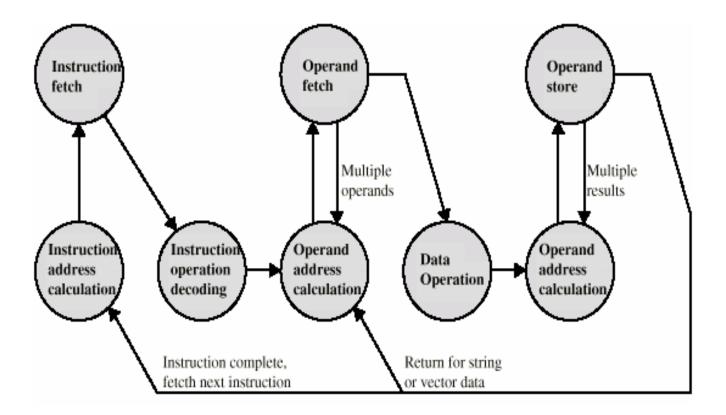

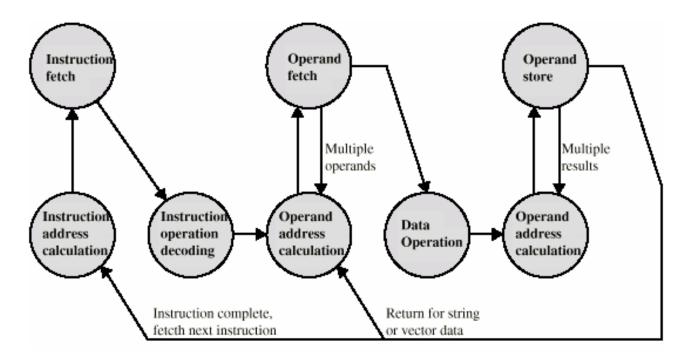

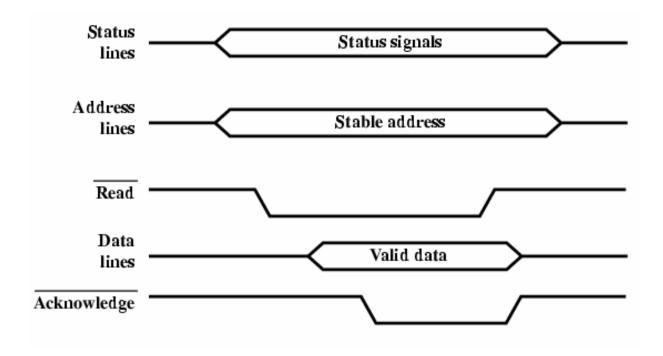

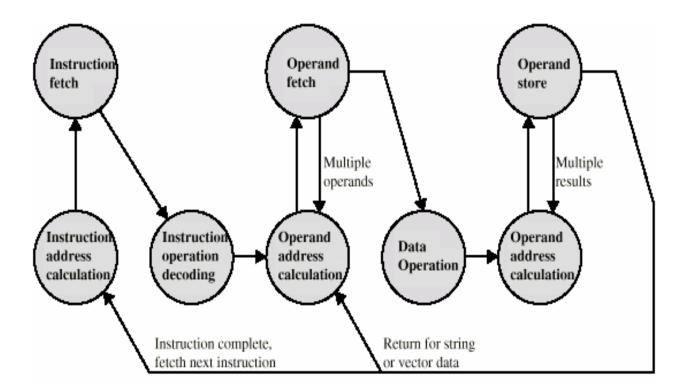

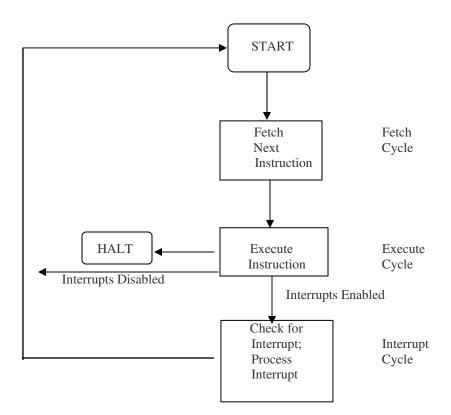

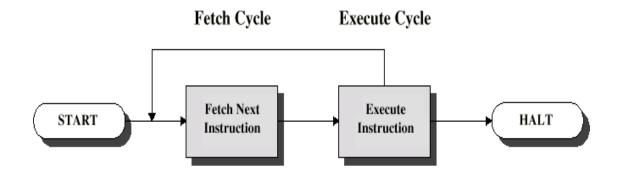

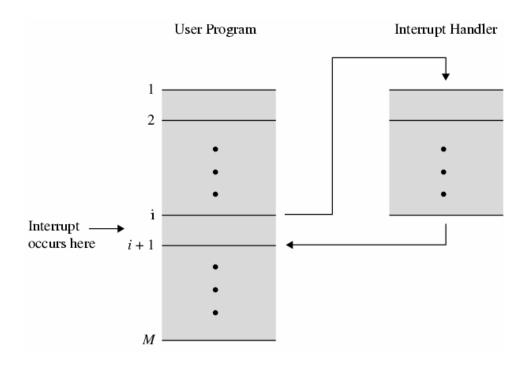

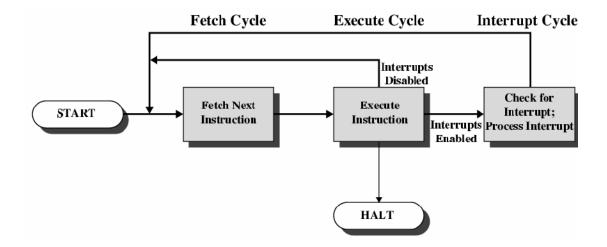

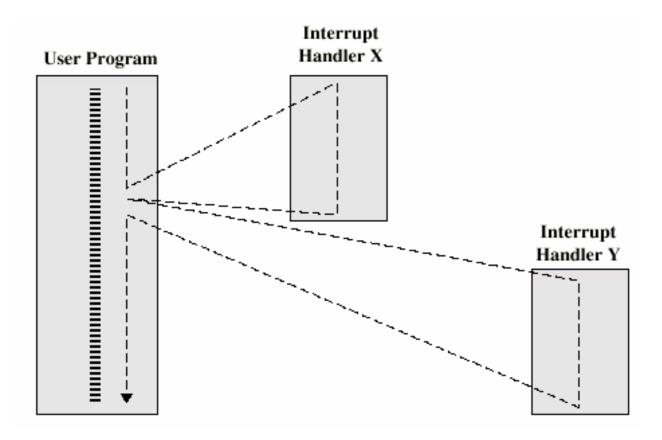

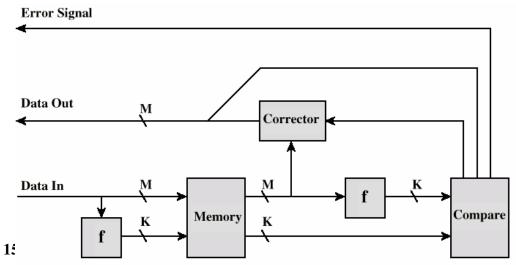

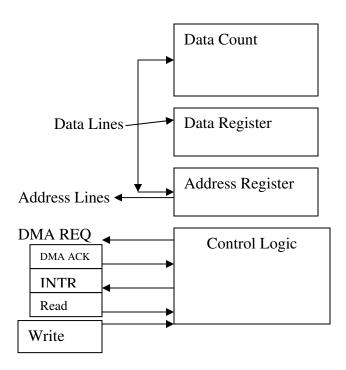

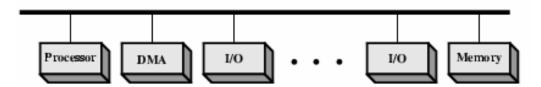

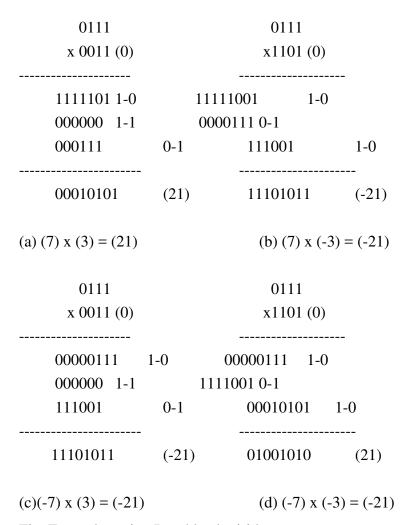

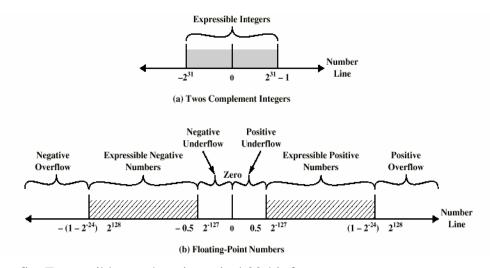

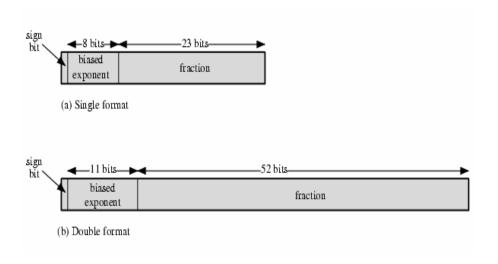

#### **Organization and architecture**